Cadence Photonics Summit and Workshop 2019 13 Nov 2019 - 14 Nov 2019, San Jose, CA, USA

# Agenda

1 Introduction

**17** RF/mm Photonics

Programmable Integrated Photonics

04 Summary & Conclusions

# Introduction

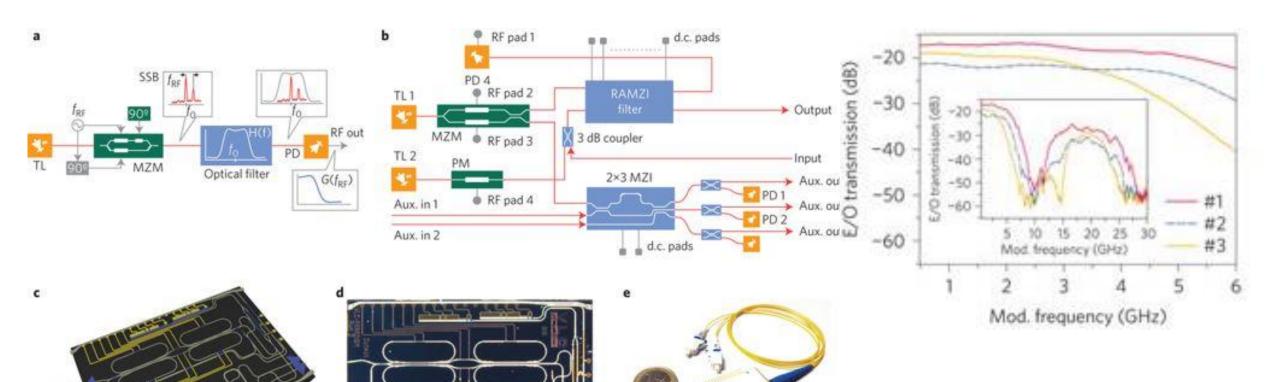

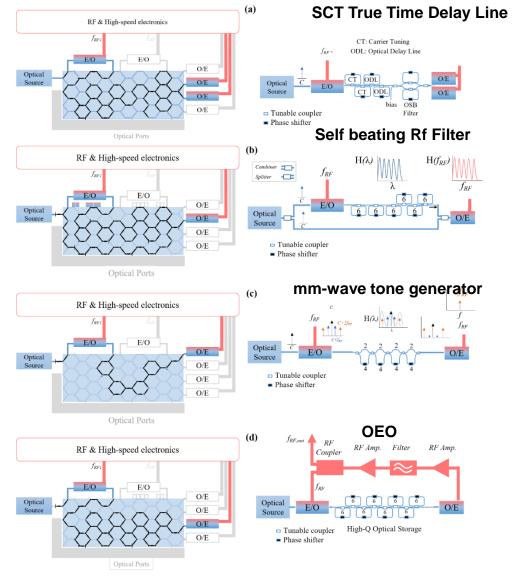

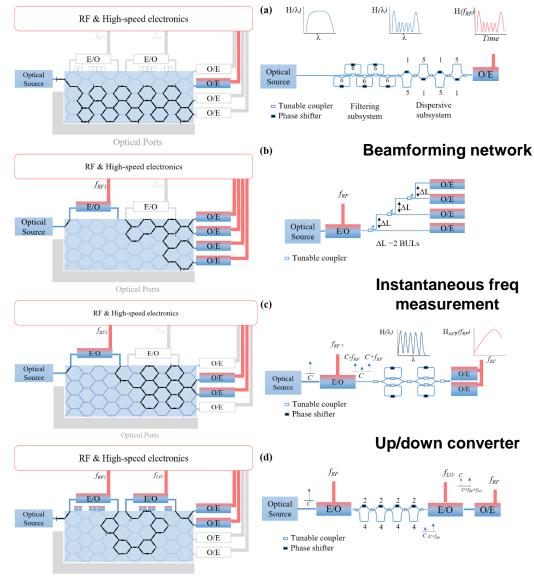

# RF/mm Photonics Integrated MWP

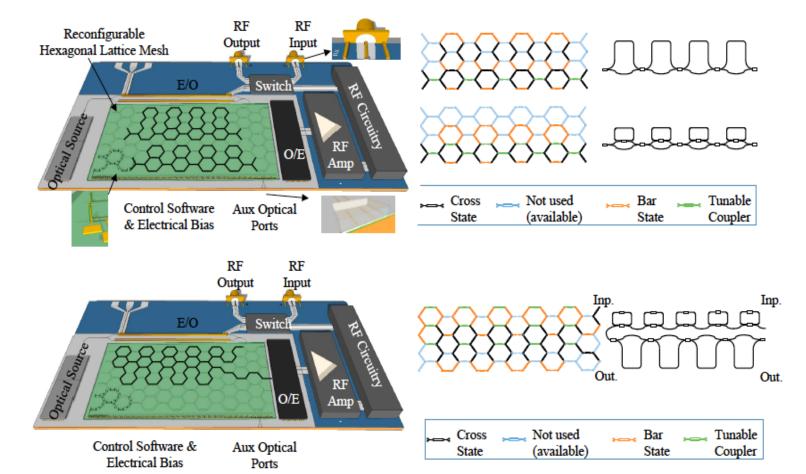

# **IMWP ASPICS**

- Designed to carry only a given functionality

- Feature some degree of flexibility enabled tuning some of its internal parameters by means of appropriate control signals.

- Fixed physical topology.

- A considerable amount of circuits reported in the literature (SOI, InP, SiN)

- Filters

- Delay lines

- RF phase shifters

- Switches, Add/Drop MuXes

- Beamformers

- Arbitrary waveform generators

- Optoelectronic oscillators

Output

Input

# **IMWP ASPICS**

# Reconfigurable Filters

# **IMWP ASPICS**

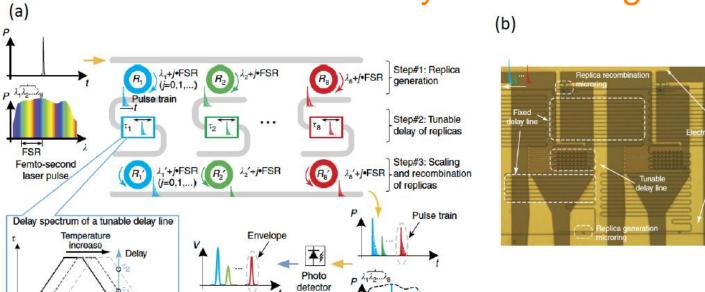

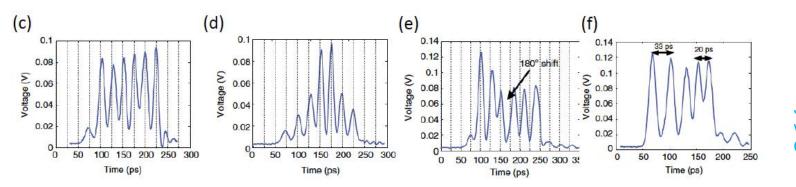

# Tunable Arbitrary waveform generator

J. Wang et al., "Reconfigurable radio-frequency arbitrary waveforms synthesized in a silicon photonic chip, " Nature Comms. 6, 5957 (2015).

u Ottawa

# **IMWP ASPICS**

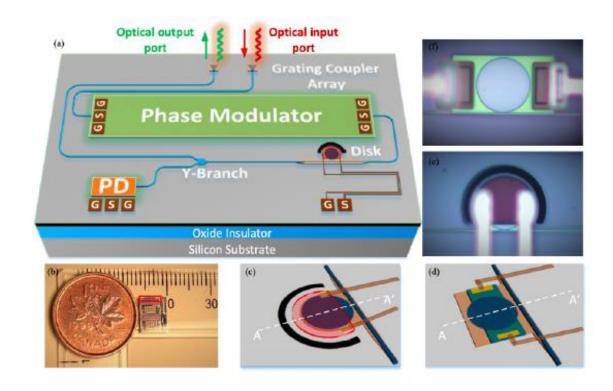

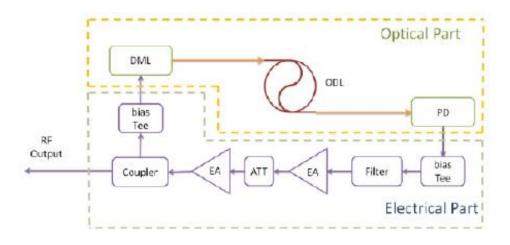

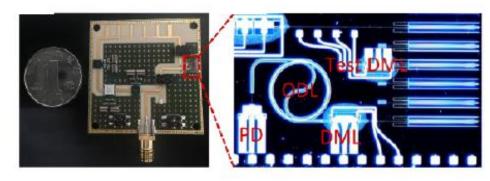

# **Optelectronic Oscillators**

J. Tang, et al., Opt. Express 26, 12257-12265 (2018).

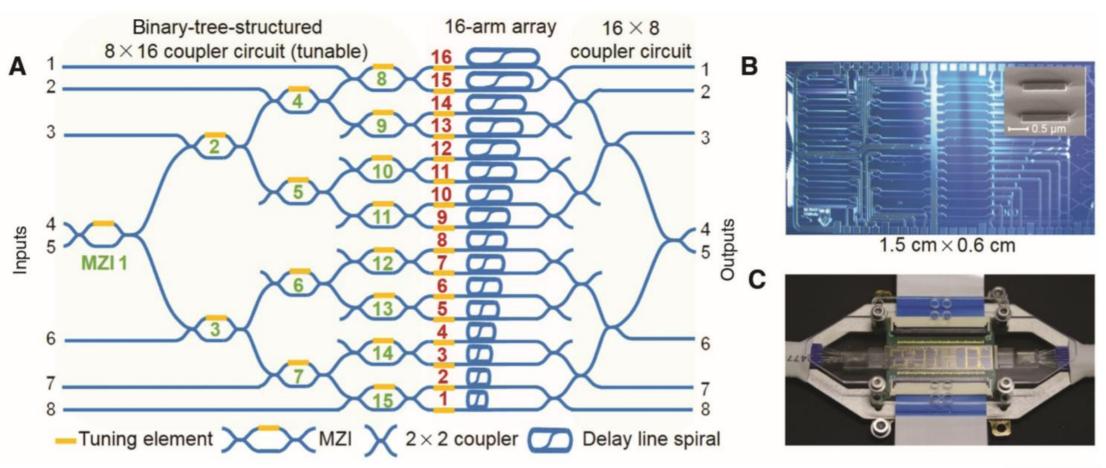

# **IMWP Multiport circuits**

# Signal Processors & Beamformers

## **IMWP ASICS**

# **iPRONICS**

# Comprehensive Reviews

2013

**LASER & PHOTONICS REVIEWS**

Laser Photonics Rev. 7, No. 4, 506-538 (2013)/DOI 10.1002/lpor.201200032

which radio frequency (RF) signals are generated, distributed, processed and analyzed using the strength of photonic techniques. It is a technology that enables various functionalities which are not feasible to achieve only in the microwave domain. A particular aspect that recently gains significant interests is the use of photonic integrated circuit (PIC) technology in the MWP field for enhanced functionalities and robustness as well as the reduction of size, weight, cost and power consumption. This article reviews the recent advances in this emerging field which is dubbed as integrated microwave photonics. Key integrated MWP technologies are reviewed and the prospective of the field is discussed.

#### Integrated microwave photonics

David Marpaung<sup>1,4,\*</sup>, Chris Roeloffzen<sup>1</sup>, René Heideman<sup>2</sup>, Arne Leinse<sup>2</sup>, Salvador Sales<sup>3</sup>, and José Capmany<sup>3,5</sup>

**REVIEW ARTICLE**

https://doi.org/10.1038/s41566-018-0310-5

nature photonics

# Integrated microwave photonics

David Marpaung 11\*, Jianping Yao 22 and José Capmany 3

2019

NATURE PHOTONICS | VOL 13 | FEBRUARY 2019 | 80-90 | www.nature.com/naturephotonics

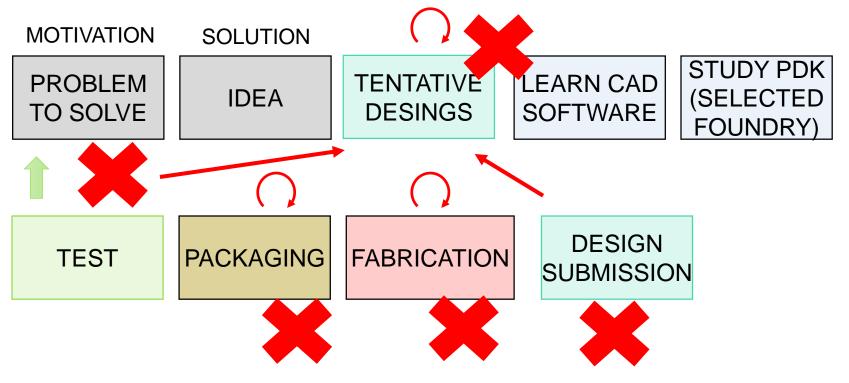

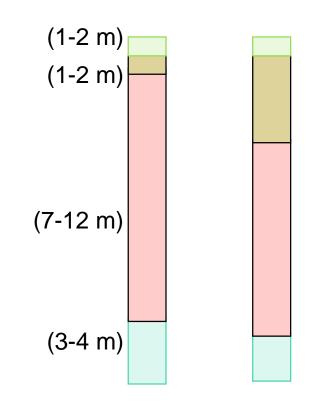

# **ASPIC Limitations**

A failure at any stage origins iteration loops in the design procedure

Time Budget (%)

**12-24 months** > 200 k€

Iteration runs no included

# ERC-ADG-2016 UMWP-Chip Project

**The main objective** of UMWP-CHIP is the design, implementation and validation of a universal integrated microwave photonics programmable signal processor, capable of performing the most important MWP functionalities featuring unique broadband and performance metrics,

# ERC-ADG-2016 UMWP-Chip Project

# Programmable Photonics

#### European Research Council

Established by the European Commission

# Target functionalities

#### Wavelength to time mapping AWG

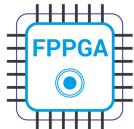

## Beyond ERC-ADG-2016→ERC-POC-2019 FPPAS

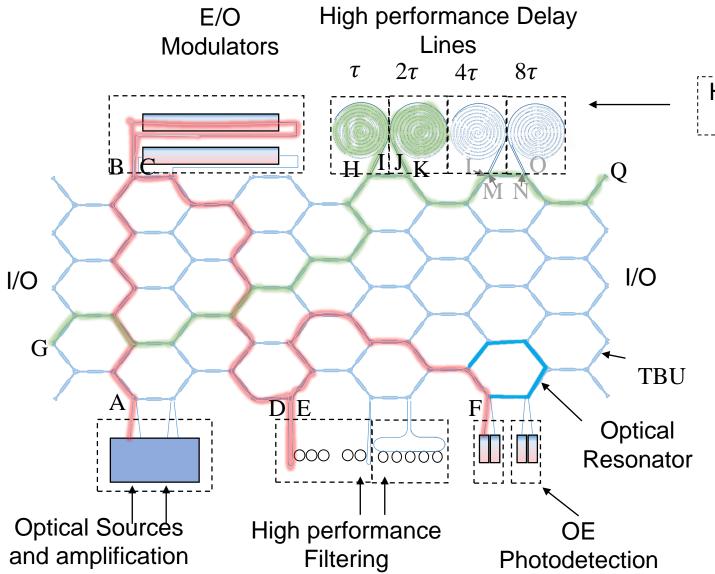

# Outsourcing special blocks outside the core

High-Performance

Building Blocks

This configuration is novel in photonics, but certainly not (with some important differences) in electronics

# Programmable Electronics vs Photonics

Some comparisons and lessons

# Reusability in ITC systems

# Re-usability / versatility / flexibility / Programmability are key features in past and future revolutions

SpaceX believes a fully and rapidly **reusable** rocket is the pivotal breakthrough needed to substantially reduce the cost and reduced development times of space access:

"60 000 000 \$ total project cost, used 1000 times, becomes three-order magnitude reduction in space missions' costs."

- In Electronics: FPGAs instead of ASICs

- In **networks**: SDN instead of ad-hoc topologies and configurations

- In radio: Software radio instead of specific RF receivers

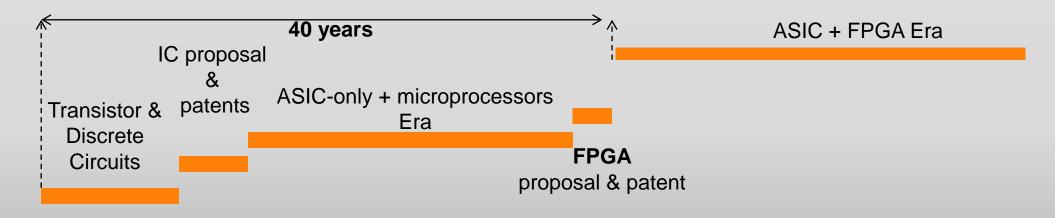

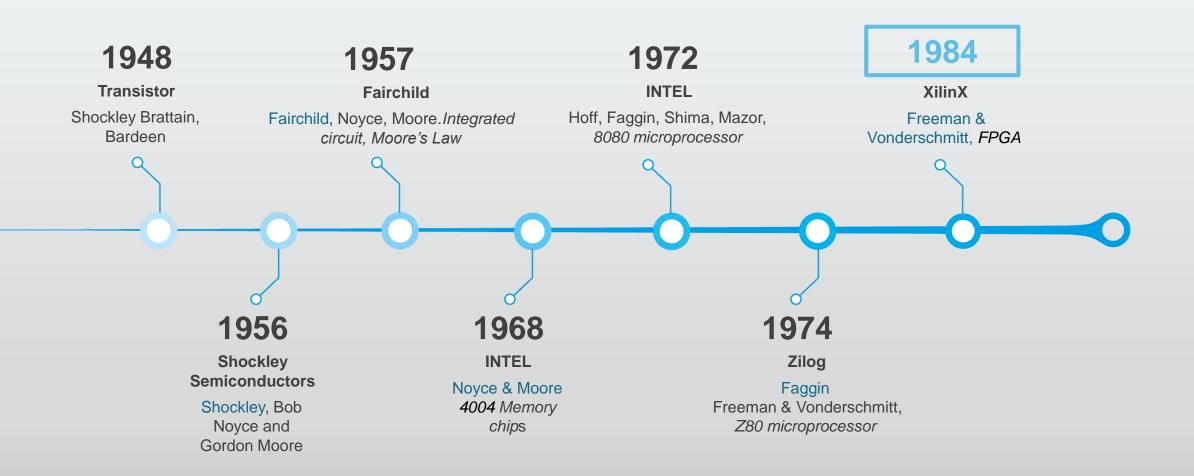

# Birth of Programmable Electronics

....By the end of the sixties, Noyce was worried about the rapid proliferation of different integrated circuits, each designed for its own special purpose.....

...Looking ahead, Noyce saw that the solution to proliferation of specialpurpose integrated circuits would be the development of general-purpose chips that could be manufactured in huge quantities and adapted ("programmed") for specific applications.

T.R. Reid "The Chip: How Two Americans Invented the Microchip and Launched a Revolution"

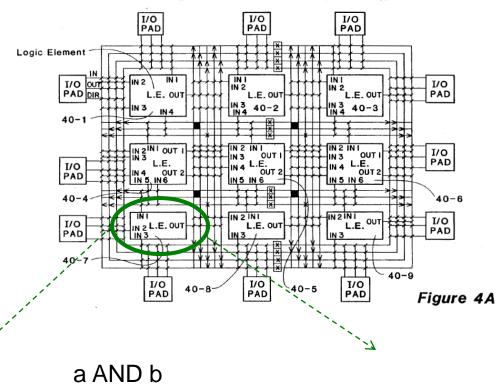

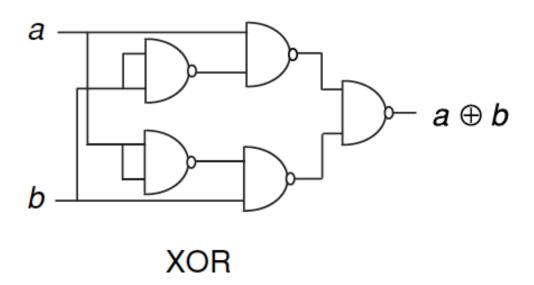

## **FPGA Fast Refresher**

Example of a 3x3 Logic Element CLA with 12 I/O pads & 3 types of L. E.'s

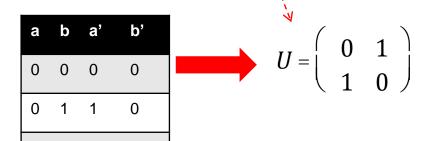

FPGAs are mainly built using irreversible 2x1 gates defined by truth tables FPGAs work with digital signals and Boolean Algebra

James Barnet

Ross Freeman

Bernie Voderschmitt

a b a AND b

0 0 0

0 1 0

1 0 0

1 1 1

| а | b | A XOR<br>b |

|---|---|------------|

| 0 | 0 | 0          |

| 0 | 1 | 1          |

| 1 | 0 | 1          |

| 1 | 1 | 0          |

a XOR b

**Electronics**

1940s

1950s

# Why FPGAS in Electronics?

**Electronic Integrated Circuit second revolution:** reconfigurable ICs.

Currently, programmable and multipurpose EICs represent more than 50% of the market.

1960s

1970s

2000s

2010s

2020s

1980s

1990s

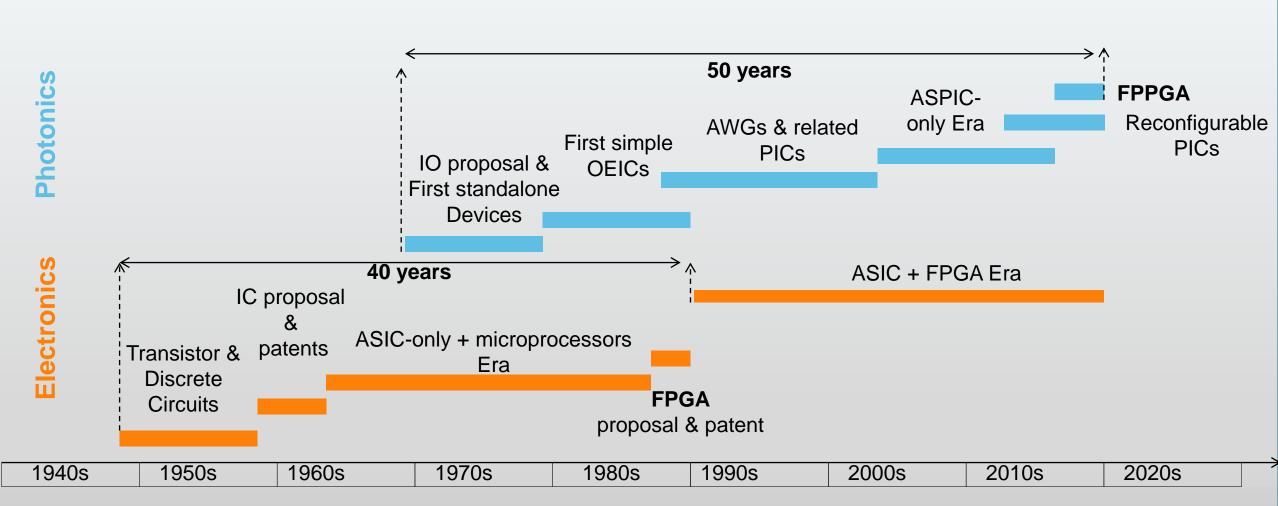

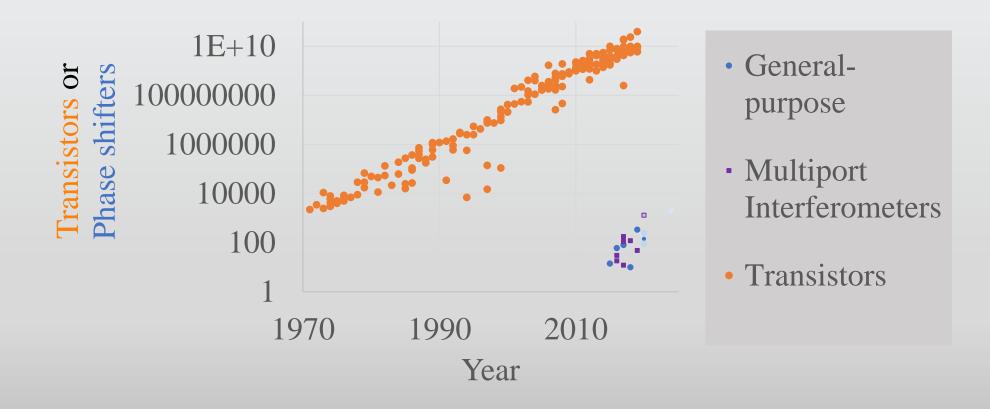

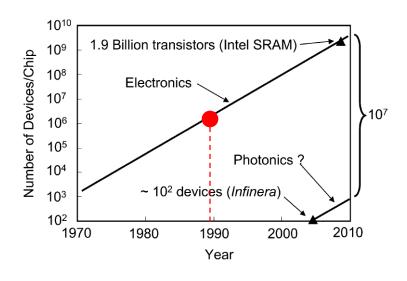

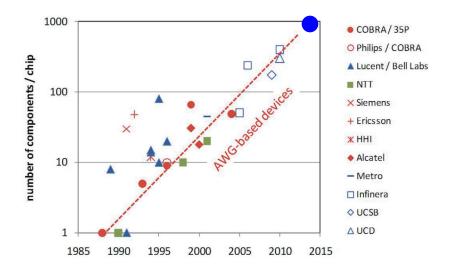

## Electronics/Photonics: a parallel evolution?

## Electronics/Photonics: a parallel evolution?

# Are we in front of another observational law in semiconductor technologies?

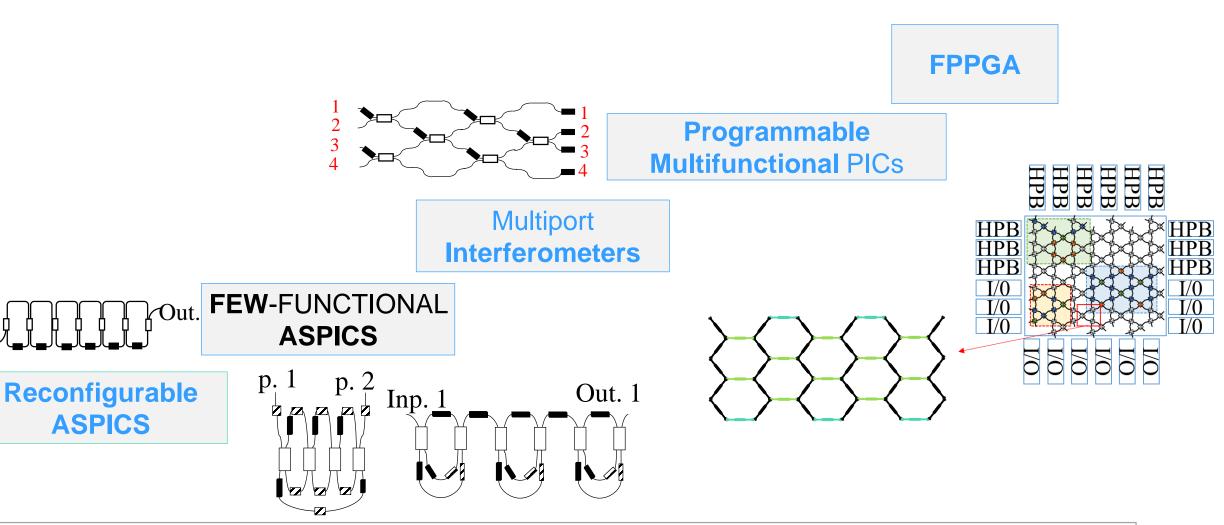

## Evolution steps in Programmable Photonics

**ASPICS**

# Some Relevant Literature in Programmable Photonics

- [1] M. Reck, A. Zeilinger, H.J. Bernstein, P. Bertani. Experimental realization of any discrete unitary operator. Phys Rev Lett 1994, 73, 58–61.

- [2] W.R. Clements, et al. Optimal design for universal multiport interferometers. Optica 2016, 3, 1460-5.

- [3] D.A.B. Miller. Self-aligning universal beam coupler. Optics Express 2013, 21, 6360-70.

- [4] D.A.B. Miller. Self-configuring universal linear optical component. Photonics Research 2013, 1, 1–15.

- [5] J. Carolan, et al. Universal linear optics. Science 2015, 349, 711.

- [6] D.A.B. Miller. Perfect optics with imperfect components. Optica 2015, 2, 747–50.

- [7] O. Graydon. Birth of the programmable optical chip. Nat Photonics 2016, 10

- [8] D. Pérez, I. Gasulla, J. Capmany J, R.A. Soref. Reconfigurable lattice mesh designs for programmable photonic processors. Opt Express 2016, 24, 12093-106.

- [9] J. Capmany, I. Gasulla, D. Pérez. Microwave photonics: The programmable processor. Nat Photonics 2016, 10, 6-8

- [10] N.C. Harris, et al. Quantum transport simulations in a programmable nanophotonic processor. Nat Photonics 2017, 11, 447-52.

- [11] L. Zhuang et al. Programmable photonic signal processor chip for radiofrequency applications. Optica 2015, 2, 854-9.

- [12] D. Pérez, et al. Multipurpose silicon photonics signal processor core, Nat Communications 2017, 8, 636.

- [13] D. Pérez et al. Silicon Photonics Rectangular Universal Interferometer. Lasers and Photon Rev 2017, 11, 1700219.

- [14] Y. Shen et al. Deep learning with coherent nanophotonic circuits. Nat Photonics 2017, 11, 441-6.

- [15] A.Ribeiro, A. Ruocco, L. Vanacker, W. Bogaerts. Demonstration of a 4 × 4-port universal linear circuit. Optica 2016, 3, 1348-57.

- [16] A. Anoni et al. Unscrambling light—automatically undoing strong mixing between modes. Light Science and Applications 2017, 6, e17110.

- [17] A. Politi et al. Silica-on-silicon waveguide quantum circuits. Science 2008, 320, 646–9.

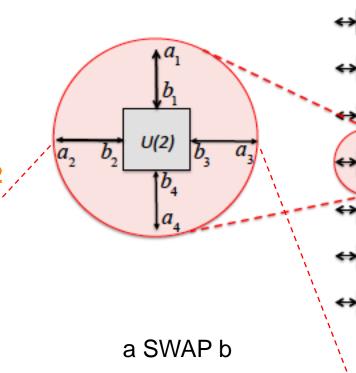

# Programmable Photonics

The Field Programmable Photonics Gate Array

FPPGAs are built using a 2D mesh of interconnected reversible 2x2 unitary gates implementing unitary analog transformations

FPPGAs work with analog signals and unitary 2x2

matrix Algebra U(2)

| Ľ   |    |     |

|-----|----|-----|

| a — |    | a'  |

| u   | 1/ | a   |

|     | X  |     |

| h   |    | h'  |

| b — |    | l D |

Reversible gates are built by transforming the Pauli Matrices, which are well known in quantum information

$$S_o = I = \begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix}; \quad S_1 = X = \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix};$$

$$S_2 = Y = \begin{pmatrix} 0 & -i \\ i & 0 \end{pmatrix}; \quad S_3 = Z = \begin{pmatrix} 1 & 0 \\ 0 & -1 \end{pmatrix}$$

The required transformations are known as Rotations

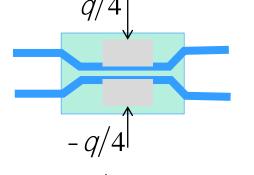

#### Rotations have simple physical implementations in integrated photonics

$$R_{X}(q) = e^{-i\frac{q}{2}X} = \begin{pmatrix} \cos(q/2) & i\sin(q/2) \\ i\sin(q/2) & \cos(q/2) \end{pmatrix}$$

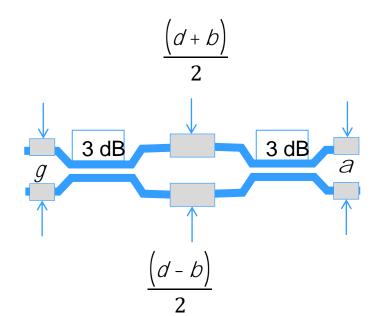

**Dual drive directional coupler**

$$R_{y}(q) = e^{-i\frac{q}{2}y} = \begin{pmatrix} \cos(q/2) & -\sin(q/2) \\ \sin(q/2) & \cos(q/2) \end{pmatrix}$$

**Dual drive 3 dB Balanced MZM**

$$R_{z}(q) = e^{-i\frac{qZ}{2}} = \begin{pmatrix} e^{-i(q/2)} & 0 \\ 0 & e^{i(q/2)} \end{pmatrix}$$

Two parallel waveguides with opposite phase shifts

Rotations are key because any unitary 2x2 matrix transformation can be obtained using the following cascade of rotation matrices:

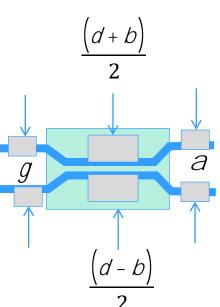

$$U = e^{jd} R_z(a) R_y(b) R_z(g)$$

$$U = e^{jd} R_z(a) R_x(b) R_z(g)$$

The former prescriptions (others are possible) allow two options for the compact photonic implementation of any unitary 2x2 matrix

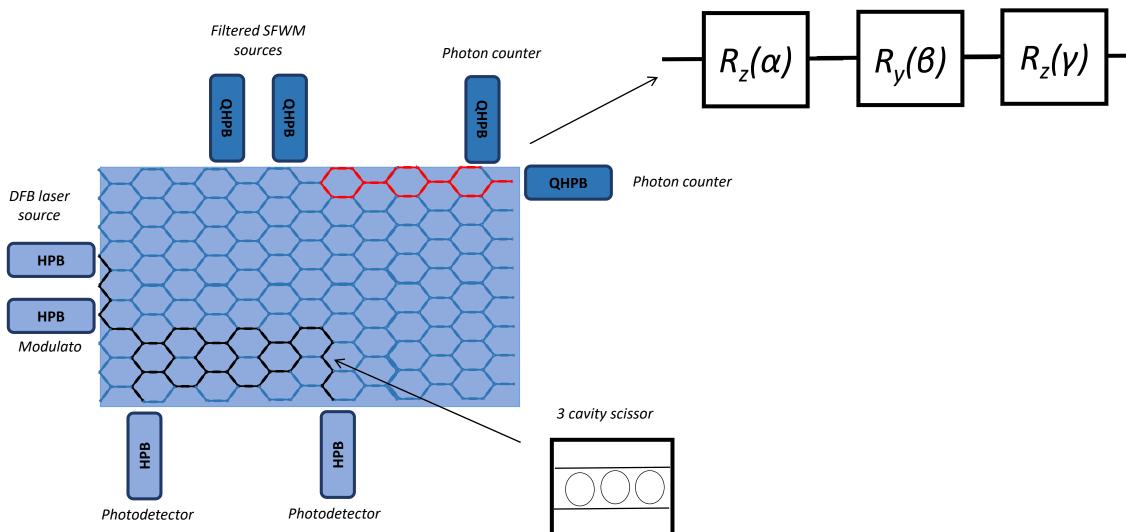

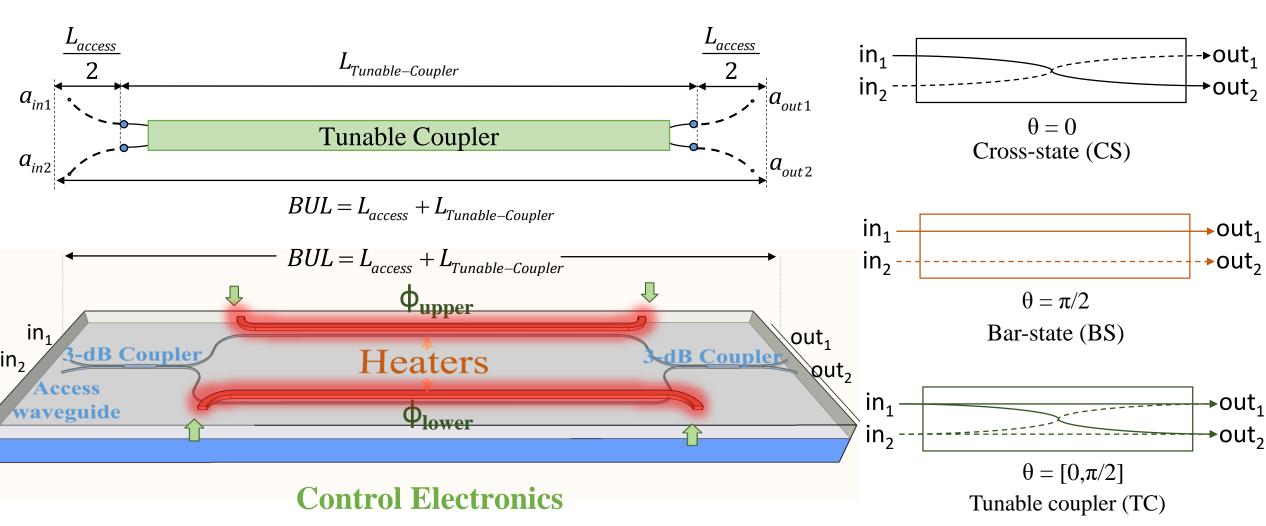

# Example: ZYZ implementation

TBUs can also be activated by carrier injection modulation

#### Feedforward signal processing architectures

Any unitary nxn transformation can be implemented by means of n(n-1)/2 two dimensional unitaries (Hurwitz, 1897).

Ueber die Erzeugung der Invarianten durch Integration.

Von

A. Hurwitz in Zürich, correspondirendem Mitgliede der Gesellschaft.

Vorgelegt von dem vorsitzenden Secretar in der Sitzung am 6. März 1897.

- Triangular (Reck et al, 1994)

- Rectangular (Clements et al, 2016)

die orthogonale Substitution

(15)

$$\begin{cases} x_{\alpha} = \cos \varphi . x'_{\alpha} + \sin \varphi . x'_{\alpha+1}, \\ x_{\alpha+1} = -\sin \varphi . x'_{\alpha} + \cos \varphi . x'_{\alpha+1}, \\ x_{\beta} = x'_{\beta}. \end{cases}$$

Nun nehme man  $\frac{n(n-1)}{2}$  Winkel

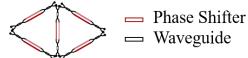

## Feedbackward signal Processing archtectures

IIR & FIR+IIR structures can be implemented by cascading full 2x2 unitary transformations and partial 1x1 and 1x2 transformations (Pérez et al 2017).

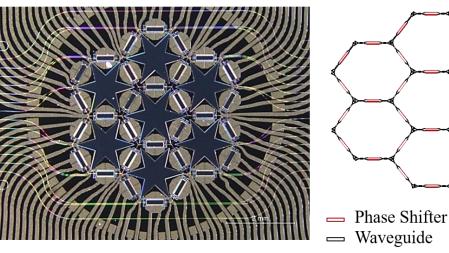

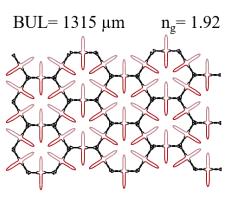

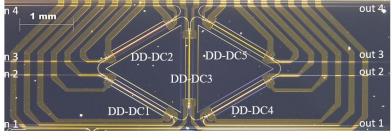

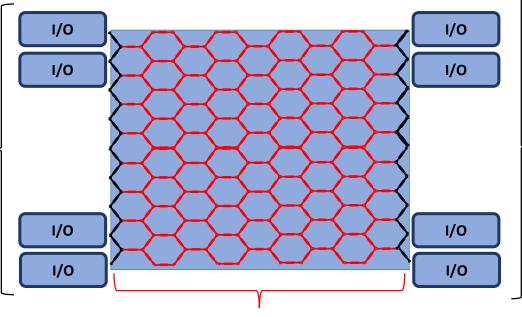

# **Core Implementations**

2 Square Cells size: 3.5 x 8.5 mm

BUL=  $3450 \, \mu m \, n_g = 1.72$

(b) 7 Hexagonal Cells size: 15 x 20 mm

Phase Shifter

Zhuang, et. al.,(2015)

BUL= 975  $\mu$ m  $n_g$ = 4.18

Pérez, et. al., (2016)

(d)

10 Hexagonal Cells size: 5.5 x 11 mm

(c)

Pérez, et. al.,(2017)

Pérez, et. al., (2019)

amplification

#### Additional Hardware Elements

DANIEL PÉREZ, IVANA GASULLA, AND JOSE CAPMANY

ITEAM Research Institute, Universitat Politècnica de València, Camino de Vera 46022 Valencia, Spain \*jcapmany@iteam.upv.es

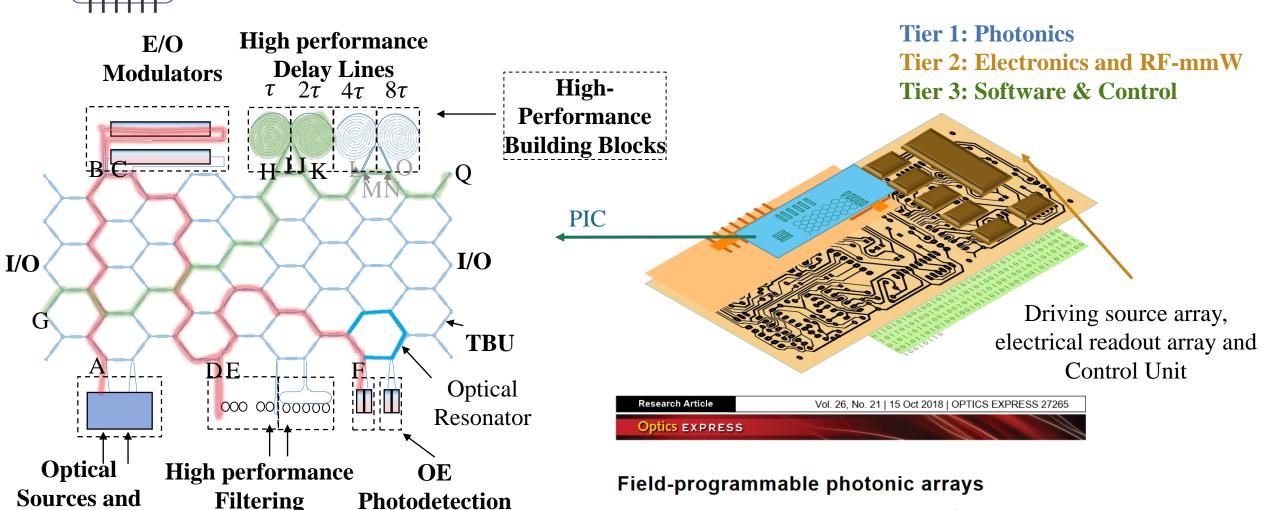

#### Tier #3 Programming/Technology Mapping/Optimization Software

Tier 3 (Software)

**Programming**

Technology Mapping

**Optimization**

Tier 2 (Electronics)

**Driving**

Control & monitorng

Tier 1

Photonics

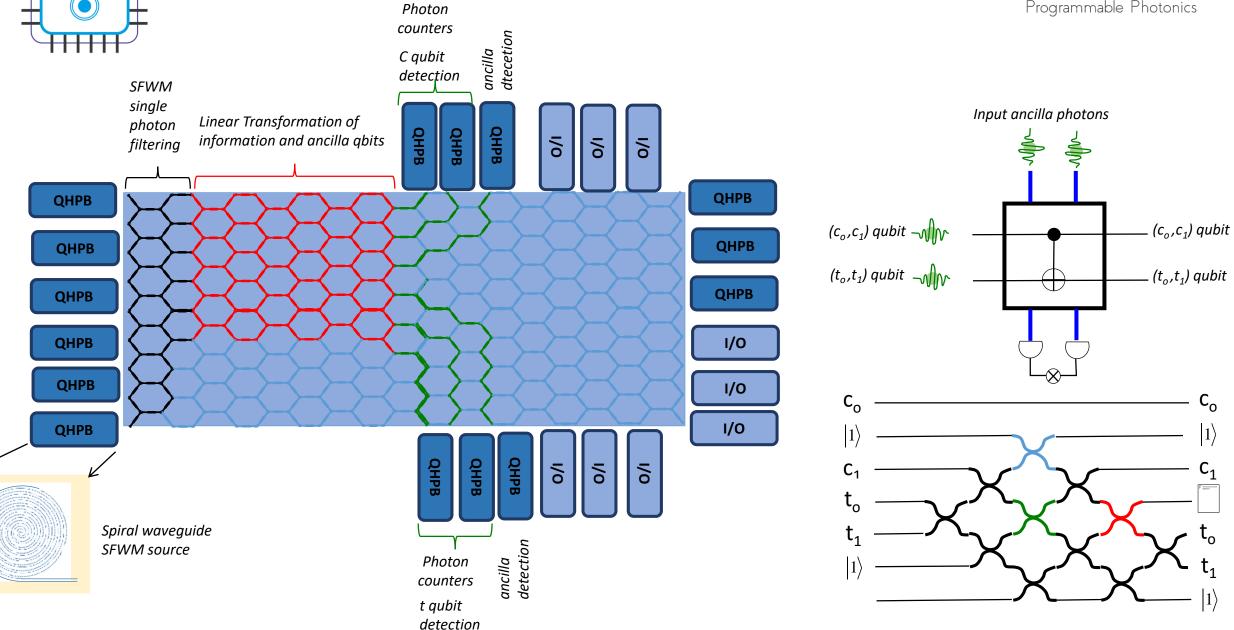

**Quantum** devices

Classical devices

Waveguide Mesh

**HPBs**

1/0

Chip-chip couplers

Chip-fiber couplers

QHPBs

#### **Quantum devices**

- NxN programmable Linear mode

transformers

- Tunable filers

- Switches Delay lines

- Photodetectors

- Optical sources

- Tunable filters

- Switches

- Modulators

- Delay lines

- Spiralled nanowire SFWM single Photon sources

- CROW single photon SFWM sources

- Integrated Bragg+ Ring cavity SFWM single Photon sources

- Integrated Single photon detectors

- -Ancilla qbit readers

**Classical devices**

- Int

## Hardware Scalability challenges

Power consumption

Accumulated optical loss

Electrical Interfacing

System integration

Optical monitoring points.

Optical crosstalk

Tuning crosstalk

Some of them can be mitigated by a smart software layer and thanks to the massively interconnected nature of the FPPGA core.

## Software Challenges

## Control and operation based on global algorithms and presets

- Requires the pre-characterization of the FPPGA core.

- Includes preset configurations, <u>auto-routing algorithms</u>, user-defined configurations.

## Control and operation based on computational optimization

### algorithms

• Enables self-configuring, self-healing, black-box optimizations and mitigates non-ideal operation of photonic components.

## High Level Description and specification language

To enable the high-level programming of the FPPGA resources.

**>-** Cross State

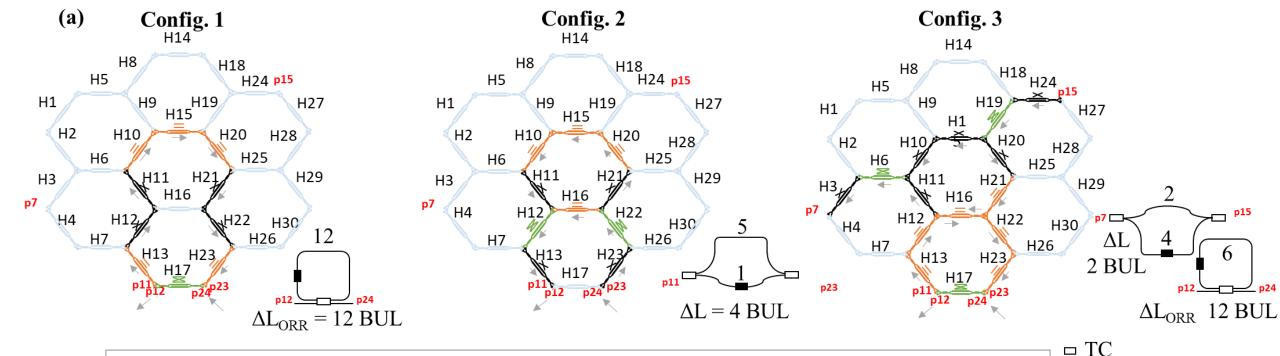

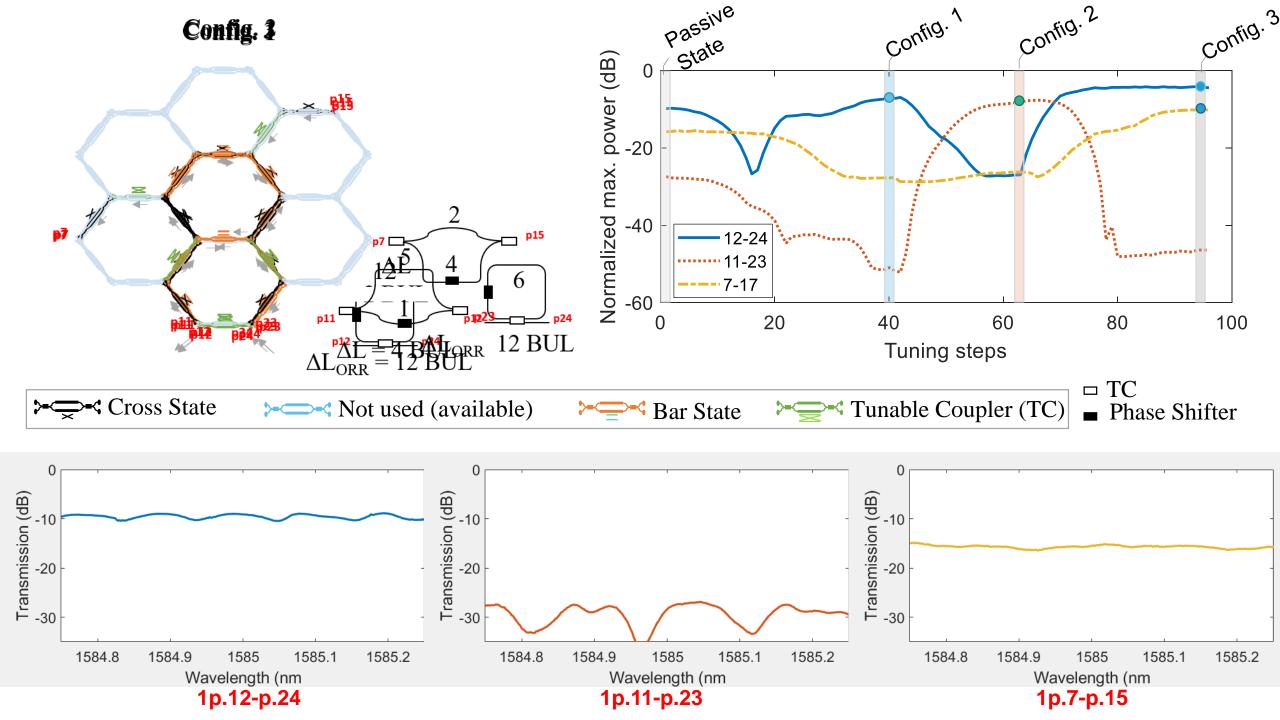

## Control and operation based on global algorithms and presets

#### **Develop / compute control vectors for each configuration:**

➤ Not used (available)

$$C_1 = [H01_U, H01_D, H02_U, H02_D, ..., H30_D]$$

$$C_2 = [H01_U, H01_D, H02_U, H02_D, ..., H30_D]$$

$$C_3 = [H01_U, H01_D, H02_U, H02_D, ..., H30_D]$$

#### Predefined pre-sets.

A. López et al., presented at ECOC 2019.

Tunable Coupler (TC)

J. Capmany, D. Pérez, "Programmable Integrated Photonics", in press Oxford University Press (2019)

Phase Shifter

Sar State

### **Applications**

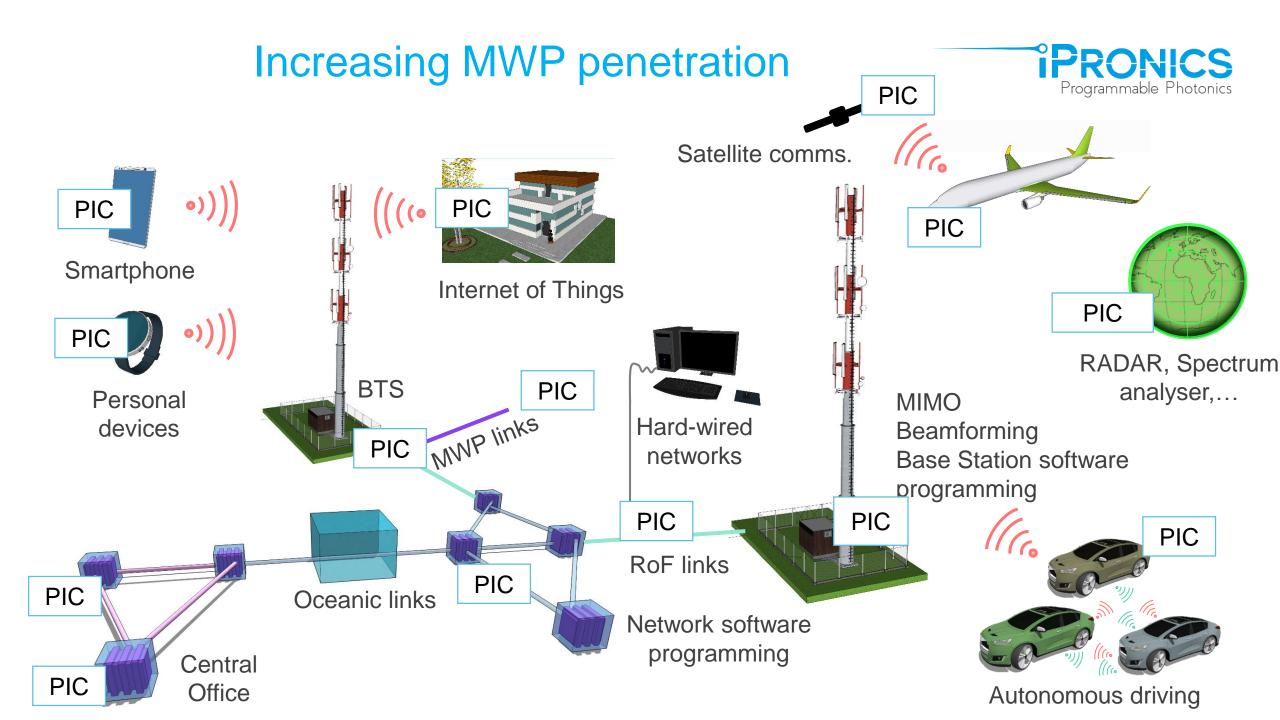

5G and Beyond

Bio instruments

**Internet of Things**

**HW** acceleration

Sensors

## More Information?, stay tuned

Jan-Feb 2020

## Summary, Conclusions & Take Away Messages

### **Summary and Conclusions**

- MWP is becoming a key enabling technology in a variety of application scenarios

- For efficient penetration into these photonic integration is key

- A considerable number of Application Specific Photonic Integrated Circuits (ASPICs) have been reported with a limited degree of functionality

- Functionality and cost efficiency can be improved by means of reconfigurability. A general purpose programmable chip for MWP applications is under current R&D

- Programmable chips with the incorporation of extra elements (IP blocks, control electronics and specialized software) enable the equivalent of the electronic FPGA

- The FPPGA relies on different basic operations (analog vs digital) compared to electronics, but these are required to handle lightwave signals

- FPPGA applications span a myriad of fields other than MWP

### Take Away Messages

Programmable Photonics is going to happen, YES or YES.

It shares commonalities with integrated Electronics

Yet it is completely different

#### INVENT THE FUTURE OF PHOTONIC INTEGRATION

www.ipronics.com

Programmable Photonic Protocols

AI-Machine Learning- algorithms

Advanced Optimization Routines

Oct 2019

## Support Wiegraphs

Examples & extra technical material

## Landmarks in programmable electronics

## Is the right time for FPPAS?

#### **Electronics**

#### **Photonics**

#### **Age of Invention**

- Cost containment

- Maximize efficiency in cost & functionality

- Eliminate waste in logic blocks

- Design efficient 2D interconnection

- Manual design, placement & routing

- Multi-Chip partitioning

#### (2015-2022)

#### Age of Invention

- Material technology platform

- Maximize efficiency in cost & functionality

- Define photonic analog gates/locks

- Design efficient 2D interconnection meshes

- Manual design, placement & routing

- Automatic control, bias, monitoring

- Interfacing with RF and electronic bias

#### **Age of Expansion**

- Moore law enabled doubling the size of largest FPGAs and halving cost per function (area less precious)

- Smaller & simpler logic units/more complex logic blocks

- Longer connections not only nearest neighbors

- Design automation (placing, routing synthesis) essential

- Increase in addressable ASIC market

#### **Age of Accumulation**

- Larger size FPGAs are no longer essential

- FPGAs include logic function + High performance predefined building dedicated blocks interconnected

- Customized products for communications

#### (1992-1999)

(1984-1991)

#### (2000-2007)

## Is the right time for FPPAS?

$\frac{Photon \ Wavelength}{Electron \ Wavelength} \gg 10^3 \Rightarrow \frac{Photonic \ Integration \ density/surface \ unit}{Electronic \ Integration \ density/surface \ unit} \gg 10^{-3}$

Integration density when FPGA was proposed 10<sup>6</sup>

Equivalent Integration density when FPPGA have been proposed 10<sup>6</sup>x10<sup>-3</sup>=10<sup>3</sup>

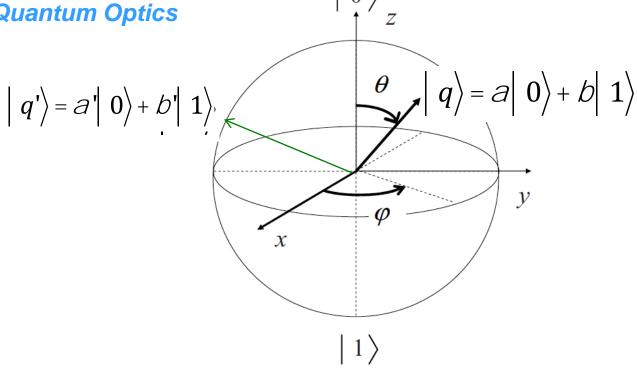

## Analog vs Digital Bit Processing

#### Digital Electronics

**Quantum Optics**

In digital electronics, bits 0 and 1 are digitally processed using the rules of Boolean Algebra Qubits are analog processed (amplitudes), using the rules of 2x2 unitary Matrix Algebra

$$y = f(a,b)$$

$a,b = \{0,1\}$

$$\left( \begin{array}{c} a' \\ b' \end{array} \right) = \left( \begin{array}{cc} u_{11} & u_{12} \\ u_{21} & u_{22} \end{array} \right) \left( \begin{array}{c} a \\ b \end{array} \right)$$

### **Example 1: Heralded CNOT Quantum Gate implementation**

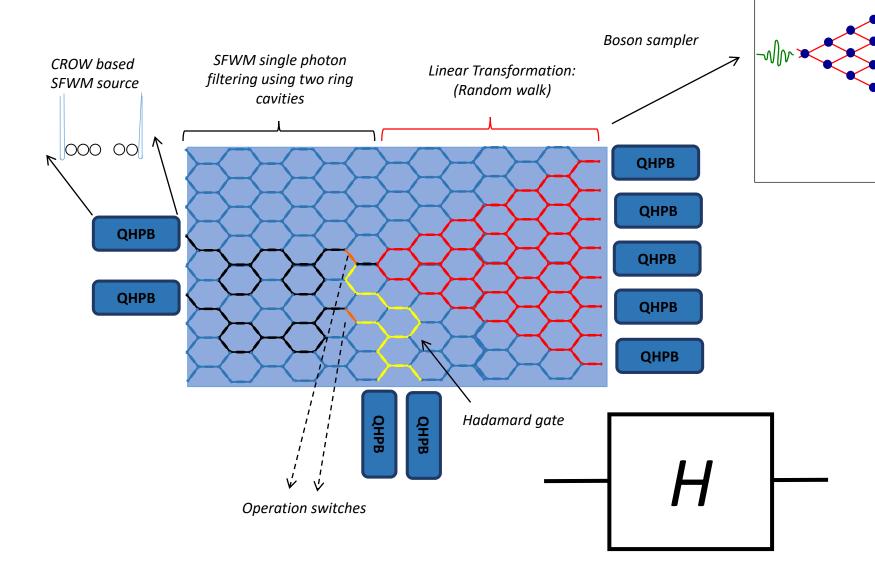

## **Example 2: Switched quantum circuits** (Boson Sampler & Hadamard gate)

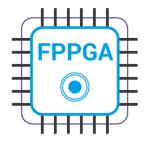

## **Example 3: Simultaneous quantum circuits** (Rotation cascade and Hadamard Gate)

Rotation Z, Rotation Y, Rotation Z cascade

#### **Example 4: Quantum Fourier Tranformer**

#### Input state

$$\left|\mathcal{Y}\right\rangle = \overset{N-1}{\underset{k=0}{\circ}} x_k \left|k\right\rangle$$

$$\begin{vmatrix} k \rangle = \begin{pmatrix} 0 \\ \vdots \\ 1 \\ \vdots \\ 0 \end{pmatrix} \quad \begin{cases} K+1 \text{ row} \\ K \end{cases}$$

### Unitary matrix for QFT

$$M = \frac{1}{\sqrt{N}} \begin{pmatrix} 1 & 1 & 1 & 1 & 1 \\ 1 & \omega & \omega^{2} & \cdots & \omega^{N-1} \\ 1 & \omega^{2} & \omega^{4} & \cdots & \omega^{2(N-1)} \\ 1 & \vdots & \vdots & \ddots & \vdots \\ 1 & \omega^{N-1} & \omega^{2(N-1)} & \cdots & \omega^{(N-1)(N-1)} \end{pmatrix}; \quad \omega = e^{i\frac{2\pi}{N}}$$

Output state

$$\left| \tilde{\psi} \right\rangle = \mathbf{QFT} \left| \psi \right\rangle = \sum_{k=0}^{N-1} \sum_{n=0}^{N-1} M_{nk} x_k \left| k \right\rangle$$

# Example 5: Simultaneous quantum & classical circuits (Rotation cascade and SCISSOR)

Rotation Z, Rotation Y, Rotation Z cascade